sequential logic 이란 출력값이 이전의 입력값과 관계가 있는 회로이다.

이 회로에는 두가지 종류가 있는데, Synchronous와 Asychronous 가 있다 둘의 차이는 Synchronous 는 clock 이 사용되고, 나머지 하나는 그렇지 않다.

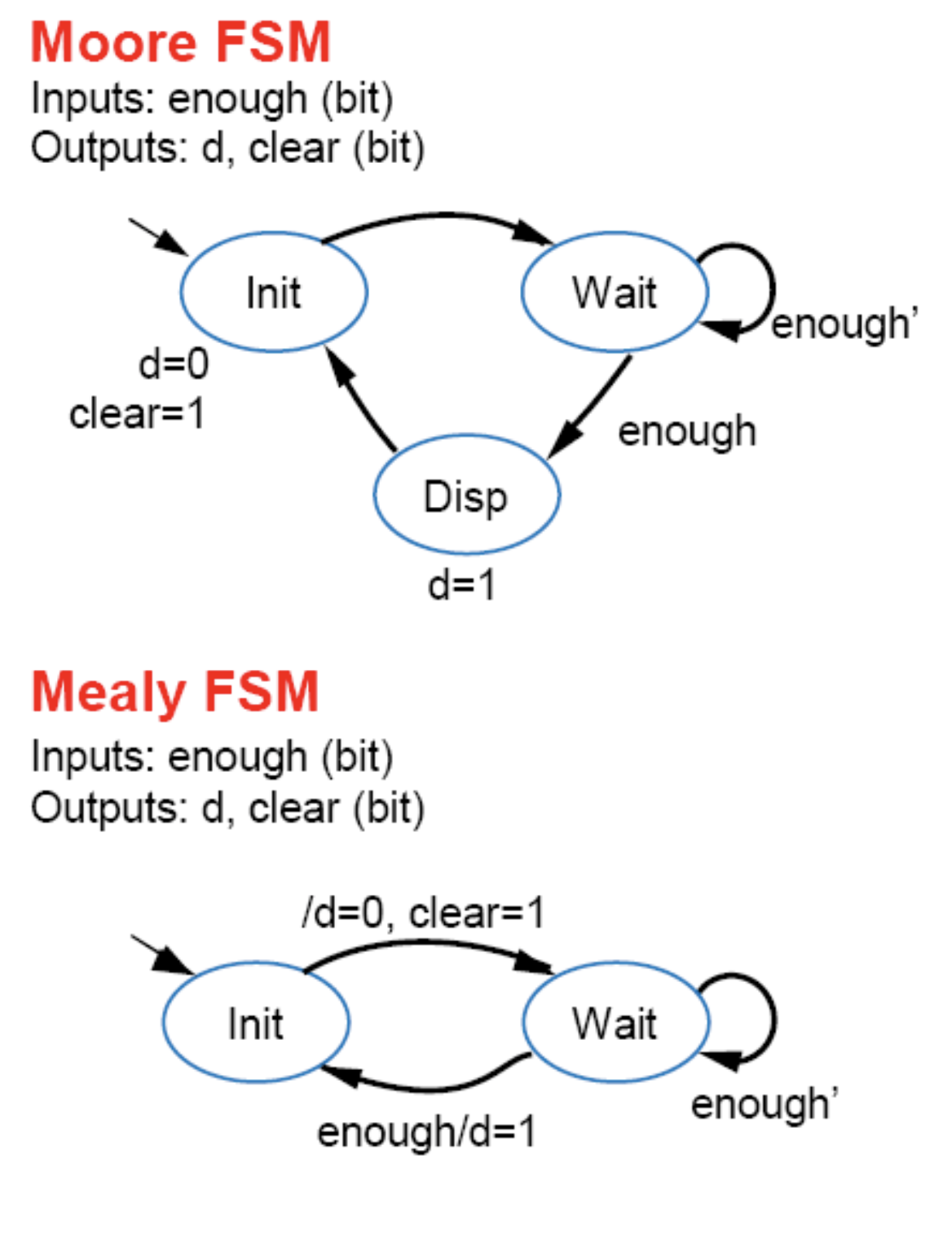

일반적인 시퀀스 로직의 회로는 아래와 같이 표현된다. FF의 앞단에 붙어있는 combination circuit은 next state를 만들어내고, FF은 현재의 상태를 저장하게 된다. 그리고 가 다음의 cl은 출력값을 계산하게 된다. 이때에 뒤의 내용을 조금 말하자면 위의 파란선, 외부입력을 출력값 계산 로직에 연결하는 경우는 mealy fsm, 아닌 경우는 moore fsm 이라고 한다.

이때의 fsm 이란?

fsm 이란 finite state machine 으로 유한한 상태의 머신이라는 뜻으로 하나의 동작을 하도록 설계한 머신이다.

이러한 fsm을 나타내는 데에는 두가지 방식이 있는데, graphical 하게 나타내는 다이어그램 방식, table 형식으로 나타내는 방법이있다.

fsm의 구성에는 상태, state 가 있고, 각각의 입력, 출력을 정의해 주어야한다. 그리고 각각의 state 에서 다른 state 로 넘어가는 transition 을 정의 해주어야한다.

오른쪽은 state digram 이다. 이를 토대로 state table 작성할 수 있다.

그리고 위처럼 표현한 표의 상태들을 이진수로 인코딩하여 나타낼 수도 있다.

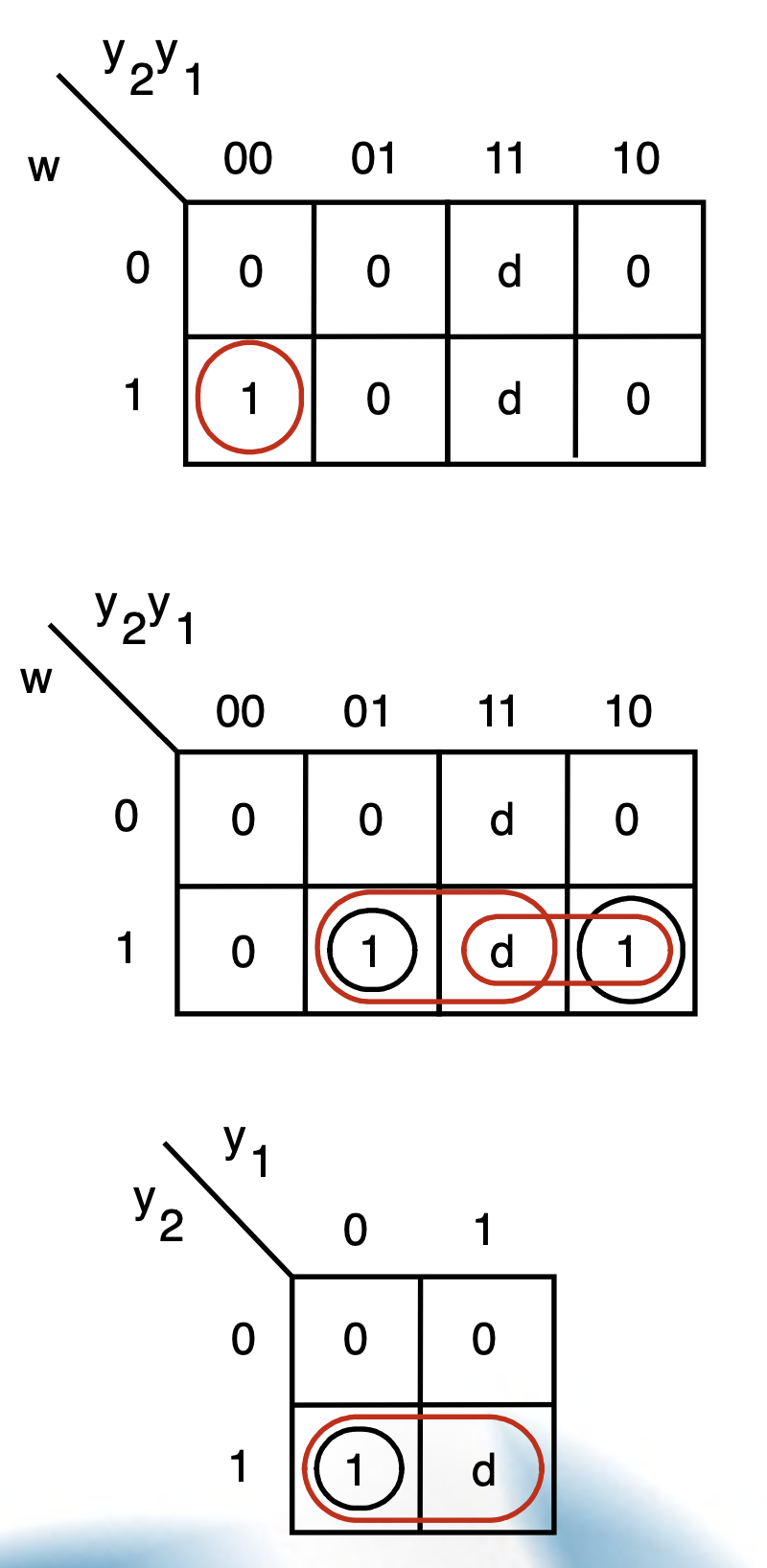

위의 d는 don't care의 의미이다. 그리고 이처럼 나타낸 후에 우리가 앞서 했던거 처럼 k-map을 그릴 수도 있다.

그리고 위에서 처럼 나타낸 k-map을 토대로 최적화를 시켜서 회로를 구현할 수 있다.

moore && Mealy fsm

이 둘의 차이는 위에서 말한바와 같이 외부의 입력을 출력을 정하는데에 있어서 사용하는지 아닌지의 차이이다.

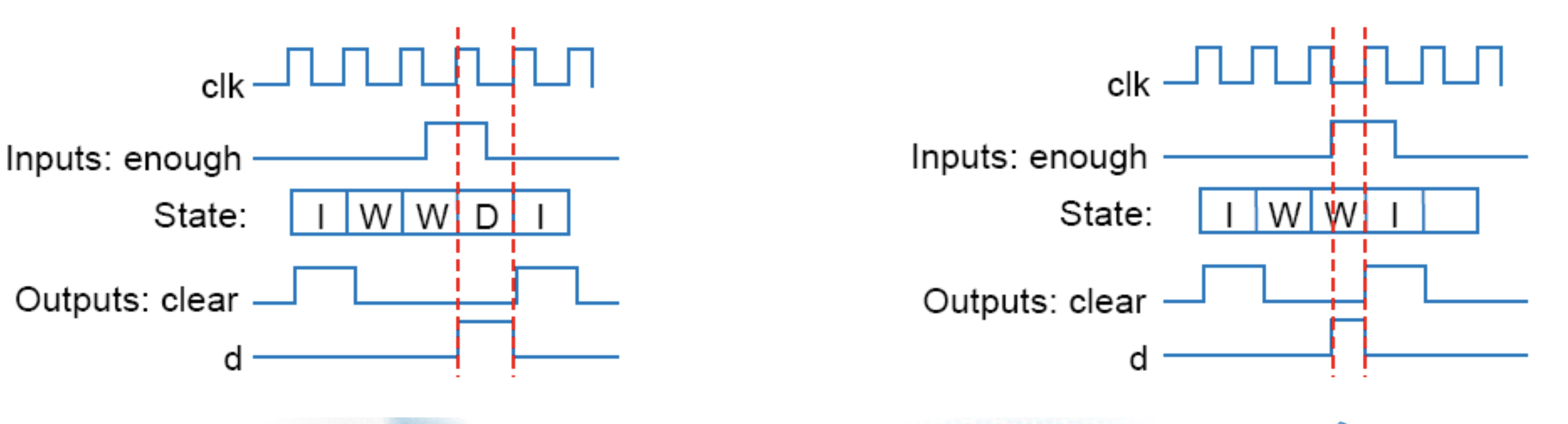

따라서 두개는 타이밍에서도 차이가 발생한다. moore의 경우는 state가 유지 되는 동안 그에 따른 출력도 유지되는 반면, mealy의 경우는 stated의 구간안에, clock이 외부입력을 읽어주어야한다.

이렇게 설계한 fsm에 따라서 table을 작성하게 되는데, 이때에 state를 이진화, encoding 하여 압축하여 나타낼 수 있다.

이렇게 압축하게 되면, state를 압축하여 표현이 가능하긴하지만, 이때의 encoding의 숫자에 따라서 optimize가 달라질 수 있다.

state를 one-hot-encoding 으로 도 구현이 가능한데, 이렇게 한다면, flipflop을 많이 쓰게 될 수 있지만, 그 뒤에 붙게되는 출력값을 계산하는 cL이 간단해지고, delay가 줄게되는 장점이 있다.

'논리회로 설계' 카테고리의 다른 글

| counter (0) | 2022.06.12 |

|---|---|

| register (0) | 2022.06.01 |

| 논회설 bit storage (0) | 2022.05.23 |

| 논회설 addition (0) | 2022.05.22 |

| mux & decoder (0) | 2022.05.16 |